ABOUT THE PRESENTE Leo Lambert Vice President & Technical Director, EPTAC

# IPC-6012

A Review, What is it? and Who Uses it?

ABOUT THE PRESENTE Leo Lambert Vice President & Technical Director, EPTAC

# **IPC-6012**

# Title:

Qualification and Performance Specification for Rigid Printed Boards

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

#### Scope

The document establishes and defines the qualification and performance requirements for the fabrication of rigid printed boards.

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

# **Purpose**

# Provides information on following Technologies:

- Single sided and double sided with and without plated through holes

- Multilayer boars with PTH, with and without buried/blind vias

- Multilayer boards containing High Density Interconnect (HDI)

- Active embedded passive circuitry printed boards.

- Metal core board.

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

- This document is a derivative document.

- To meet the IPC requirements, the following issues need to be addressed.

- Design Criteria, based upon the 2200 series documents.

- Laminate selection based upon the 4101 document.

- This continues from board fabrication through manufacturing and shipping to the customer.

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

- This document is used:

- By the board shops to manufacture the raw boards.

- to qualify and inspect the raw boards coming from the board shops

- to define the AQL for inspection of incoming boards.

- This document also defines the test coupons to be used to evaluate different characteristics of the raw board.

ABOUT THE PRESENTE

Leo Lambert

Vice President & Technical

Director, EPTAC

- This document list 26 different test from IPC-TM-650 to evaluate the product.

- It also lists all the IPC document from the design requirements, to adhesives, base materials, solder mask, testing procedures etc.

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

• It defines the different plating requirements for the various class of products being manufactured, as shown in Table 3-3

ABOUT THE PRESENTI Leo Lambert Vice President & Technical Director, EPTAC

# **Table 3-3**

## Table 3-3 Surface and Hole Copper Plating Requirements for Through-Holes, Blind, and Buried Vias > 2 Layers 1

|                                 | Class 1         | Class 2         | Class 3         |  |

|---------------------------------|-----------------|-----------------|-----------------|--|

| Copper – average <sup>2</sup>   | 20 μm [787 μin] | 20 μm [787 μin] | 25 μm [984 μin] |  |

| Minimum thin areas <sup>3</sup> | 18 μm [709 μin] | 18 μm [709 μin] | 20 μm [787 μin] |  |

| Minimum Wrap⁴                   | AABUS           | 5 µm [197 µin]  | 12 μm [472 μin] |  |

Note 1. Does not apply to microvias. Blind vias have greater than 1:1 aspect ratio.

Note 2. Copper plating (1.3.4.2) thickness **shall** be continuous and wrap from hole walls onto outer surfaces. Refer to IPC-A-600 for discussion on copper plating thickness for hole walls.

Note 3. For Class 3 PBs having a drilled hole diameter  $\leq 0.35$  mm [0.0138 in] and having an aspect ratio > 3.5:1, the minimum thin area copper plating in the hole **shall** be 25  $\mu$ m [984  $\mu$ in].

Note 4. Wrap copper plating for filled PTHs and vias shall be in accordance with 3.6.2.11.1.

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

- The type of coating to be used has to be defined in the contract between the manufacturer and the user as it is inspected to the requirement of this document

- The final finishes and coating requirements are defined in this document.

ABOUT THE PRESENTER Leo Lambert Vice President & Technical Director, EPTAC

# **Table on Finishes**

Table 3-2 Final Finish and Coating Requirements

| Code  | Finish                                                                                  | Thickness                                | Applicable<br>Acceptability<br>Specification | Marking Code <sup>1</sup> |

|-------|-----------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------|---------------------------|

| S     | Solder Coating over Bare Copper                                                         | Coverage & Solderable <sup>2</sup>       | J-STD-006                                    | b0                        |

| b1    | Lead-Free Solder Coating over Bare<br>Copper                                            | Coverage & Solderable <sup>2</sup>       | J-STD-006                                    | b1                        |

| Т     | Electrodeposited Tin-Lead (fused) -<br>minimum                                          | Coverage & Solderable <sup>2</sup>       | J-STD-006                                    | b3                        |

| X     | Either Type S or T                                                                      | As indicated by code                     |                                              |                           |

| TLU   | Electrodeposited Tin-Lead Unfused -<br>minimum                                          | 8.0 μm [315 μin]                         | J-STD-006                                    | b3                        |

| G     | Gold for edge-board connectors and areas not to be soldered - minimum                   | Class 1 and Class 2<br>0.8 µm [31.5 µin] | None                                         |                           |

|       |                                                                                         | Class 3<br>1.25 µm [49.21 µin]           |                                              | b4                        |

| GS    | Gold Electroplate on areas to be<br>soldered –maximum³                                  | 0.45 μm [17.72 μin]                      | None                                         | b4                        |

| GWB-1 | Gold Electroplate for areas to be wire bonded (ultrasonic) – minimum                    | 0.05 μm [1.97 μin]                       | None                                         | b4                        |

|       | Electrolytic nickel under gold for areas<br>to be wire bonded (ultrasonic) -<br>minimum | 3 μm [118 μin]                           | None                                         | b4                        |

ABOUT THE PRESENTE

Leo Lambert

Vice President & Technical

Director, EPTAC

# **Section 3.3 Visual**

This section covers visual examination of the printed board such as:

- Edges

- Laminate imperfections

- Measling

- Crazing

- Delamination/blistering

- Foreign inclusions

- Weave exposure

- Bow and Twist

- etc

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

# 3.4 Printed Board Dimensional Requirements

# Internal Inspection of:

- Hole Size

- Pattern Accuracy and PatternFeature Accuracy

- Annular Ring Breakout, internal and external

Leo Lambert Vice President & Technical Director, EPTAC

#### 3.5 Conductor Definition

#### • Discusses:

- Width and Thickness

- Spacing

- Imperfections

- Nick and pinholes

- SMT land

- Wire bond pads

- Edge connector lands

- Dewetting/nonwetting

- Final finish

ABOUT THE PRESENTE

Leo Lambert

Vice President & Technical

Director, EPTAC

# 3.6 Structural Integrity

Discusses structural integrity for thermally stress evaluation of test coupons defined in 3.6.2

- Plating integrity and voids

- Laminate voids and cracks

- Delamination

- Etchback

- Smear removal

- Hole breakout, internal and external

- Lifted lands

- Plating thickness

- Foil thickness, internal and external

- Metal cores

ABOUT THE PRESENTER Leo Lambert Vice President & Technical Director, EPTAC

| B                                                                                                            | Table 0-0 Flated flote integrity After Stress                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |                                                                                                          |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Property                                                                                                     | Class 1                                                                                                                                                                                                                                                                                                                                                                                                                                    | Class 2                                                                                                  | Class 3                                                                                                  |  |  |  |  |  |

| Copper voids                                                                                                 | Three voids allowed per hole.<br>Voids in the same plane are not<br>allowed. No void <b>shall</b> be<br>longer than 5% of board<br>thickness. No circumferential<br>voids greater than 90° allowed.                                                                                                                                                                                                                                        | One void allowed per<br>specimen provided the<br>additional microsection criteria<br>of 3.6.2.2 are met. | One void allowed per<br>specimen provided the<br>additional microsection criteria<br>of 3.6.2.2 are met. |  |  |  |  |  |

| Plating folds/inclusions                                                                                     | The minimum copper thickness in Table 3-2 must be met. For positive etchback, measurements should follow the topography of the dielectric. When negative etchback results in folds in the copper plating, the copper thickness <b>shall</b> meet the minimum requirements as measured from the face of the internal layer, negative etchback limits <b>shall</b> not be exceeded. See Figure 3-11. Sample must be microetched to evaluate. |                                                                                                          |                                                                                                          |  |  |  |  |  |

| Burrs and nodules <sup>2</sup>                                                                               | Allowed if minimum hole diameter is met.                                                                                                                                                                                                                                                                                                                                                                                                   | Allowed if minimum hole diameter is met.                                                                 | Allowed if minimum hole diameter is met.                                                                 |  |  |  |  |  |

| Glass fiber protrusion                                                                                       | Allowed, See 3.6.2.11.                                                                                                                                                                                                                                                                                                                                                                                                                     | Allowed. See 3.6.2.11.                                                                                   | Allowed, See 3.6.2.11.                                                                                   |  |  |  |  |  |

| Wicking (Copper Plating)                                                                                     | 125 µm [4,921 µin] maximum                                                                                                                                                                                                                                                                                                                                                                                                                 | 100 μm [3,937 μin] maximum                                                                               | 80 μm [3,150 μin] maximum                                                                                |  |  |  |  |  |

| Innerlayer inclusions<br>(inclusions at the interface<br>between internal lands and<br>through hole plating) | Allowed on only one side of hole wall at each land location on 20% of each available land.                                                                                                                                                                                                                                                                                                                                                 | None allowed.                                                                                            | None allowed.                                                                                            |  |  |  |  |  |

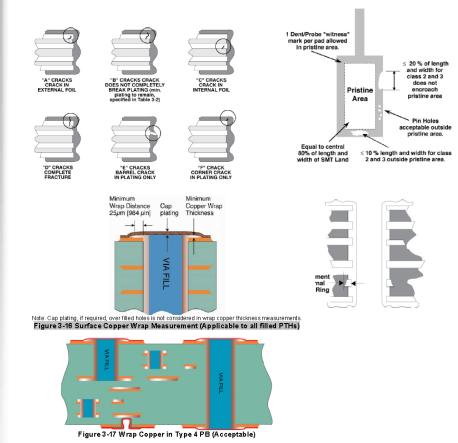

| Internal foil cracks <sup>1</sup>                                                                            | "C" cracks allowed on only one<br>side of hole provided<br>it does not extend through foil<br>thickness.                                                                                                                                                                                                                                                                                                                                   | None allowed.                                                                                            | None allowed.                                                                                            |  |  |  |  |  |

| External foil cracks <sup>1</sup> (Type "A," "B" and "D" cracks)                                             | "D" cracks not allowed. "A"<br>and "B" cracks allowed.                                                                                                                                                                                                                                                                                                                                                                                     | "D" and "B" cracks not allowed. "A" cracks allowed.                                                      | "D" and "B" cracks not<br>allowed. "A" cracks allowed.                                                   |  |  |  |  |  |

| Barrel/Comer cracks <sup>1</sup> (type<br>"E" and "F" cracks)                                                | None allowed.                                                                                                                                                                                                                                                                                                                                                                                                                              | None allowed.                                                                                            | None allowed.                                                                                            |  |  |  |  |  |

Table 3-6 Plated Hole Integrity After Stress

16

ABOUT THE PRESENTER Leo Lambert Vice President & Technical Director, EPTAC

A = 1.414 x Radius of PTH

B = Diameter of PTH

# Illustrations

Leo Lambert Vice President & Technical Director, EPTAC

# 3.7 Solder Mask

• Solder mask coverage, cure, adhesion, thickness, etc.

Table 3-10 Solder Mask Adhesion

|                                                                              | Maximum Percentage Loss<br>Allowed |         |         |

|------------------------------------------------------------------------------|------------------------------------|---------|---------|

| Surface                                                                      | Class 1                            | Class 2 | Class 3 |

| Bare Copper                                                                  | 10                                 | 5       | 0       |

| Gold or Nickel                                                               | 25                                 | 10      | 5       |

| Base Laminate                                                                | 10                                 | 5       | 0       |

| Melting Metals (Tin-lead<br>plating, fused tin-lead, and<br>bright acid-tin) | 50                                 | 25      | 10      |

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

# 3.8 Through 3.10

- 3.8 Electrical Requirements

- 3.9 Cleanliness

- 3.10 Special Requirements

- 3.11 Repair

- 3.12 Rework

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

#### **4.0 Quality Assurance Provisions**

#### This section address

- Qualification testing

- Acceptance testing

Leo Lambert Vice President & Technical Director, EPTAC

# **Test Table**

PB Type: PBs without PTHs (Type 1) and with PTHs (Types 2-6) are classified as follows:

*Type 1—Single-Sided PB*

Type 2—Double-Sided PB

*Type 3—Multilayer PB without blind or buried vias*

*Type 4—Multilayer PB with blind and/or buried vias*

Type 5—Multilayer metal core PB without blind or buried vias

*Type 6—Multilayer metal core PB with blind and/or buried vias*

Table 4-1 Qualification Test Coupons Types 2,3,5 Types 4, 6 PB3 Test Type 1 Visual¹ ΑII Solderability Surface<sup>1</sup> M2, M5 Hole S1,S6 S1,S6 Dimensional<sup>1</sup> ΑII Х Physical Plating Adhesion<sup>1</sup> N1, N4, N5 N1, N4, N5 N1, N4, N5 Bond Strenath A2, A3, A6 Construction Integrity PTH Prior to A1, A4, A5 Design Req. Design Stress Additional Dimensions A1, A4, A5 Req. PTH After Stress Thermal Stress A1, A4, A5 Design Req. Horizontal micro (Metal Core) Rework B4, B5 A1, B4, B5 Simulation B3, B6 Design Req

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

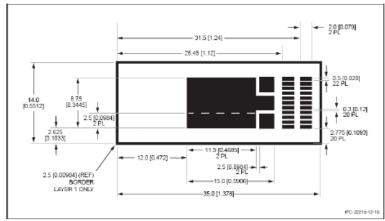

# From 2221 12.4.7 Coupon M

- **(Surface Mount Solderability Optional)** The coupon shall be as shown in Figure 12-18.

- This coupon may be used to evaluate solderability of surface mount lands to IPC-J-STD-003 requirements. If it is used, the test method and performance criteria shall be specified in the procurement documentation.

Figure 12-18 Test Coupon M. Surface Mounting Solderability Testing, mm [in]

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

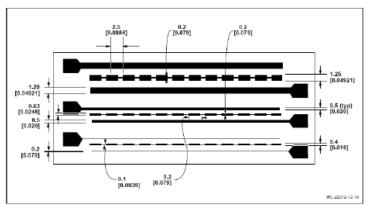

# From 2221 12.4.8 Coupon N

(Peel Strength, Surface Mount Bond Strength - Optional for SMT) This coupon shall be as shown in Figure 12-19. Coupon N is used for evaluating peel strength and may be used to evaluate the bond strength of surface mount lands. If it is used, the test method and performance criteria shall be specified in the procurement documentation.

Figure 12-19 Test Coupon N, Surface Mounting Bond Strength and Peel Strength, mm [in]

ABOUT THE PRESENTER Leo Lambert Vice President & Technical Director, EPTAC

# Thank You Any Questions?

ABOUT THE PRESENTER

Leo Lambert

Vice President & Technical

Director, EPTAC

## **Further Information**

For questions regarding this webinar, please contact Leo Lambert at <a href="mailto:leo@eptac.com">leo@eptac.com</a> or call at 800-643-7822 ext 215

For information on any of EPTAC's or IPC's Certification Courses, please visit our website at <a href="http://www.eptac.com">http://www.eptac.com</a>

Fore ease of getting the EPTAC website,

We now have an APP

get our APP at

www.Eptacapp.com