Leo Lambert Vice President & Technical Director, EPTAC

## IPC -7095C Design and Assembly Process Implementation For BGAs

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

eptac webinarseries

## **Overview**

With the introduction of BGA components, things had to change:

- New design

- New assembly process

- New repair process

- New inspection techniques

All information in this presentation is adapted from the IPC-7095C document

Leo Lambert Vice President & Technical Director, EPTAC

Scope

- Covers the challenges for implementing all types of BGA components

- Information in document focuses on inspection, repair and reliability with BGA components

Leo Lambert Vice President & Technical Director, EPTAC

## Purpose

- To provide practical and useful information to users of BGA components

- Target audience is managers, design and process engineers, operators and technicians

Leo Lambert Vice President & Technical Director, EPTAC

## Intent

- This document identifies many of the issues involved which will influence the implementation of a robust BGA assembly process

- The accept/reject criteria is found in J-STD-001 and IPC-A-610

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## **Applicable Documents**

There is a list of • 27 IPC Documents • 16 JEDEC Documents

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## **Why BGA Components**

- Peripheral devices with 1.00 mm pitch have become commonplace, however these packages cannot accommodate more than 84 pins.

- Larger pin count devices require lead pitches on 0.65 mm, 0.5 mm or 0.3 mm

- Therefore at these pitches leads are very fragile and susceptible to damage.

- The BGA eliminated lead and coplanarity problems

Leo Lambert Vice President & Technical Director, EPTAC

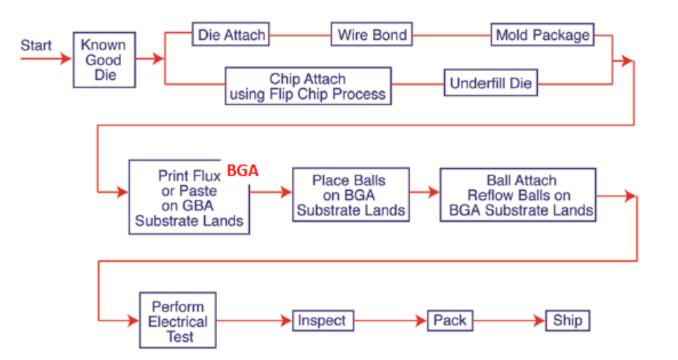

### BGA Package Manufacturing Process

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## Infrastructure

• Land Patterns and circuit board considerations.

### Technology comparison

| МСМ     | Technology Description        | Attributes                               |

|---------|-------------------------------|------------------------------------------|

| Type 1  | Common Technology Package     | Multiple same type chips, in plane       |

| Type 1S | Common Technology Package     | Multiple same type chips, stacked        |

| Type 1F | Common Technology Package     | Multiple same type chips, folded         |

| Type 2  | Mixed Technology Package      | Mixed IC technology package, in plane    |

| Type 2S | Mixed Technology Package      | Mixed IC technology package, stacked     |

| Type 2F | Mixed Technology Package      | Mixed IC technology package, folded      |

| Туре 3  | System in Package             | Mixed ICs and discrete devices, in plane |

| Type 3S | System in Package             | Mixed ICs and discrete devices, stacked  |

| Type 4  | Optoelectronic System Package | Mixed technology for optoelectronics     |

|         |                               |                                          |

Figure 3-4 MCM type 2S-L-WB

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

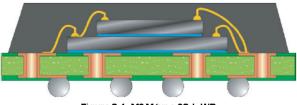

## **Conductors Between BGA Connections**

• This gets into the size of the BGA and the number of traces which can be used between the balls of the BGA component

#### Table 3-2 Number of escapes vs. array size on two layers of circuitry

|            |             | Number of Conductors Between Vias (• •) |      |       |  |

|------------|-------------|-----------------------------------------|------|-------|--|

|            |             | 1                                       | 2    | 3     |  |

| Array Size | Total Leads | • •                                     | •  • | •   • |  |

| 14 X 14    | 196         | 192                                     | 196  | 196   |  |

| 16 X 16    | 256         | 236                                     | 256  | 256   |  |

| 19 X 19    | 361         | 272                                     | 316  | 352   |  |

| 21 X 21    | 441         | 304                                     | 356  | 400   |  |

| 25 X 25    | 625         | 368                                     | 436  | 496   |  |

| 31 X 31    | 961         | 464                                     | 556  | 640   |  |

| 35 X 35    | 1225        | 528                                     | 638  | 736   |  |

Leo Lambert Vice President & Technical Director, EPTAC

## Conductor Width to Pitch Relationship

Figure 3-5 Conductor width to pitch relationship

Leo Lambert Vice President & Technical Director, EPTAC

### **eptac** Webinarseries

## Infrastructure

- Assembly Equipment Impact

- Stencil Requirements

- Inspection Requirements

- Test

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## **Limitations and Issues**

- Visual inspection

- Moisture sensitivity

- Rework

- Cost

- Availability

- Voids in BGA

- Open joints

- Head-on-Pillow phenomenon

- Standards and their adoption

- Reliability concerns

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## **Limitations and Issues**

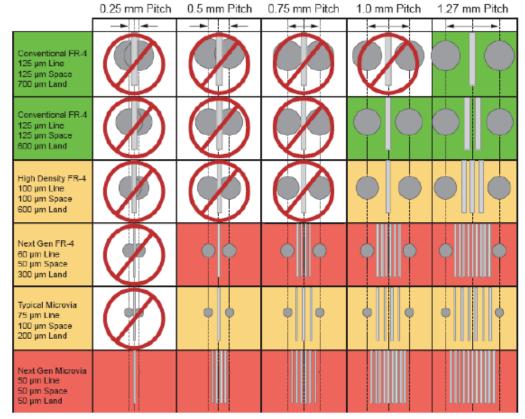

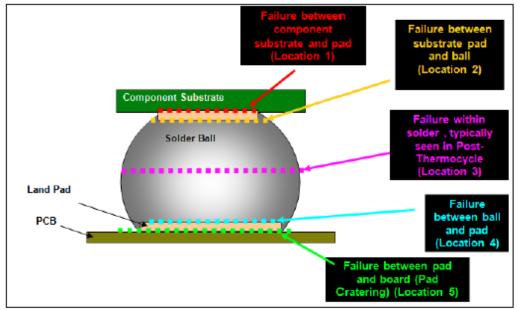

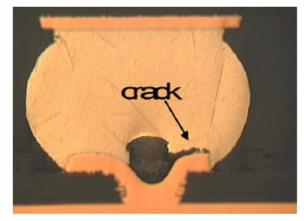

3.5.8 Pad Cratering – defined as a separation of the pad from the PCB resin/weave composite or within the composite immediately adjacent to the pad, also know as "laminate crack"

Figure 3-9 Examples of Pad Cratering

Leo Lambert Vice President & Technical Director, EPTAC

### **eptac** Webinarseries

## **Limitations and Issues**

Figure 3-10 Various Possible Failure Modes for a BGA Solder Joint

ABOUT THE PRESENTER

## **Component Consideration**

- 4.1 Semiconductor Packaging Comparison and Drivers

- 4.2 Die Mounting in the BGA Package

Leo Lambert Vice President & Technical Director, EPTAC

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

### eptac webinarseries

## **BGA Standards**

## 4.3.1 Industry Standard

- BGA Package

- Fine Pitch BGA Package

- Die Size

- Ball Pitch

- Land Pattern Approximation

- BGA package outline

- Ball size relationships

- Package on Package

- Coplanarity

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## **Component Consideration**

4.4 Component Packaging Style Consideration

- Base Material

- Solder ball Alloy

- Ball attachment process

- Ceramic BGA, Column Grid Array

- Multiple Die packaging

Leo Lambert Vice President & Technical Director, EPTAC

### **eptac** Webinarseries

## **Component Consideration**

- 4.5 BGA component and Sockets

- 4.6 Construction Materials

- 4.7 Package Design

- 4.8 Acceptance Criteria and shipping Format

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## **Boards and Other Mounting Structures**

Section 5.0 covers:

- Laminates or mounting structures

- Laminate properties

- Surface Finishes

- Solderable Coatings

Leo Lambert Vice President & Technical Director, EPTAC

|                                                     |                                                                            |                                                                                                                 |                                |                                          | - Allo                                | P                                        |

|-----------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------|---------------------------------------|------------------------------------------|

|                                                     | Table 5-2                                                                  | Key attributes                                                                                                  | for various board              | surface finishes                         |                                       |                                          |

|                                                     | HASL<br>SnPb/SnCu*                                                         | OSP                                                                                                             | Electroless<br>NI/Immersion AU | E lectrolytic<br>Ni/E lectroplated<br>AU | Immersion<br>Silver**                 | Immersion<br>Tin                         |

| Shelf Life proper<br>Handling                       | 1 Year                                                                     | 6 Months                                                                                                        | > 1 Year                       | > 1 Year                                 | 6 Months                              | 6 Months                                 |

| Handling                                            | Normal                                                                     | Avoid physical<br>contact                                                                                       | Normal                         | Normal                                   | Avoid physical contact                | Avoid physical contact                   |

| SMT land Surface<br>topology                        | Domed/Flatter                                                              | Flat                                                                                                            | Flat                           | Flat                                     | Flat                                  | Flat                                     |

| Multiple assembly<br>reflow cycles                  | Good,<br>although<br>intermetallics<br>increase/need<br>robust<br>laminate | Fair, better with<br>thick coatings;<br>may see bare<br>copper if<br>reflowed with<br>lead-free solder<br>paste | Good                           | Good                                     | Good                                  | Good                                     |

| Hole fill after<br>multiple reflow<br>cycles        | No Concerns                                                                | May have<br>problems after<br>2x reflow.                                                                        | No concerns                    | No concerns                              | No concerns                           | May have<br>problems after<br>2x reflow. |

| Use on thick PCBs                                   | Barrels<br>difficult to fill<br>and clear                                  | PTH fill<br>concerns                                                                                            | Improved barrel<br>reliability | Improved barrel<br>reliability           | PTH fill<br>concern                   | PTH fill<br>concern                      |

| Use in thin PCBs                                    | No, prone to<br>warping/Avoid                                              | Yes                                                                                                             | Yes                            | Yes                                      | Yes                                   | Yes                                      |

| Solder joint<br>reliability                         | Good                                                                       | Good                                                                                                            | BGA "black pad"<br>concerns    | Gold<br>embrittlement<br>concerns        | Planar<br>microvoid<br>concerns       | Good                                     |

|                                                     |                                                                            |                                                                                                                 | Sporadic bi                    | rittle fracture                          |                                       |                                          |

| Card edge contacts                                  | Additional<br>plating<br>operation                                         | Additional<br>plating operation                                                                                 | Additional plating operation   | No additional<br>plating                 | Additional<br>plating<br>operation    | Additional<br>plating<br>operation       |

| Wire bonding                                        | No                                                                         | No                                                                                                              | No                             | Yes                                      | No                                    | No                                       |

| Test point probing                                  | Good                                                                       | Poor, unless<br>solder applied<br>during assembly                                                               | Good                           | Good                                     | Good                                  | Good                                     |

| Exposed Copper<br>after Assembly                    | No                                                                         | Yes                                                                                                             | No                             | No                                       | No                                    | No                                       |

| Switches/Contacts                                   | No                                                                         | No                                                                                                              | Yes                            | Yes                                      | Yes                                   | No                                       |

| Waste Treatment<br>and Safety in PCB<br>Fabrication | Poor/Fair                                                                  | Good                                                                                                            | Fair                           | Fair                                     | Poor                                  | Good                                     |

| Process Control                                     | Thickness<br>control<br>concerns                                           | Fair                                                                                                            | Phosphorus<br>content concerns | Gold thickness<br>control concerns       | Micro-etch and<br>plating<br>concerns | Tin whisker<br>concerns                  |

| Coating<br>thickness/µm                             | 0.8 - 0.38                                                                 | 0.2 - 0.5                                                                                                       | 3-7/0.05-0.10                  | .8 – 2.5                                 | 0.07 - 0.10                           | 1.0 – 1.3                                |

| General Cost<br>Comparison                          | 1                                                                          | 0.4 - 0.6                                                                                                       | 2.0 - 3.0                      | 1.2 – 1.5                                | 1.1 – 1.6                             | ~0.8                                     |

\* Tin copper alloy is the preferred alloy for lead-free HASL

\*\* For reflow operation >1 year if sealed in Moisture Membrane Bag (MMB)

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

### **Boards and Other Mounting Structures**

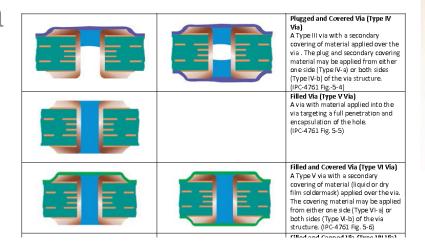

## 5.4 Solder Mask

- Wet and Dry Film mask

- Photoimageable soldermask

- Via Protection

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

# Exactly September 2015 September 201

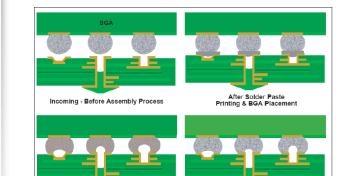

Figure 6-20 Via-in-pad process descriptions

Post Reflow Soldering

IPC-20908-0-

During Reflow Soldering

Figure 6-22 Microvia in pad voiding

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## PCB Assembly Design Considerations

6.4 Impact of Wave Solder on Top Sided BGAs

6.5 Testability and test points

6.6 Other design for Mfg issues

6.7 Thermal Management

6.8 Documentation and electronic Data Transfer

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

### Septac Webinar series Assembly of BGA to the PCB - Section 7

- Solder paste

- Stencils

- Powder Size

- Paste volume

- Component Placement and Insp

## • Reflow and profile

### Table 7-1 Particle size comparisons

| Solder paste type | Mesh      | Maximum particle size [µm] |

|-------------------|-----------|----------------------------|

| Type 2            | -200/+325 | 75                         |

| Type 3            | -325/+500 | 53                         |

| Type 4            | -400/+500 | 38                         |

| Type 5            | -500      | 25                         |

Leo Lambert Vice President & Technical Director, EPTAC

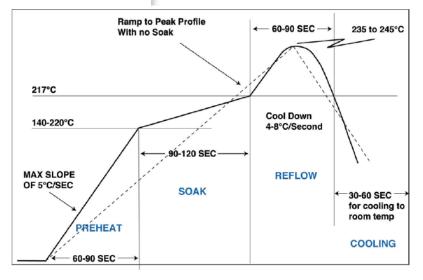

## **Time and Temp Profiles**

Table 7-3 Profile comparison between SnPb and SAC Alloys

| Profile Topic                                                     | SnPb Alloy Profile | Mixed/Backward<br>Compatibility Profile | Pb-Free Alloy<br>(SAC)/Forward<br>Compatibility Profile |  |

|-------------------------------------------------------------------|--------------------|-----------------------------------------|---------------------------------------------------------|--|

| Alloy Solidus temperature                                         | 1830C              | 1830C/2200C                             | 217-220oC                                               |  |

| Alloy soldering temp range                                        | 210-220oC          | 228-232oC                               | 235-245oC                                               |  |

| Minimum peak reflow temperature                                   | 205°C              | 228oC                                   | 230°C                                                   |  |

| Component ramp up rate                                            | 2-4oC / second *   | 2-4oC / second *                        | 2-4oC / second *                                        |  |

| Component ramp down rate                                          | 2-6oC / second *   | 2-6oC / second *                        | 2-6oC / second *                                        |  |

| Soak or preheat activation<br>temperature                         | 100-180oC *        | 100-180oC *                             | 140-220oC *                                             |  |

| Soak or preheat activation time                                   | 60—120 seconds*    | 60–120 seconds *                        | 60–150 seconds *                                        |  |

| Dwell time above liquidus                                         | 60—90 seconds      | 60–90 seconds                           | 60–90 seconds                                           |  |

| Dwell time at peak temp.                                          | 20 seconds max     | 20 seconds min                          | 20 seconds max                                          |  |

| * Verify with the supplier<br>** Coolest Temperature on the board |                    |                                         |                                                         |  |

## **Time and Temp Profiles**

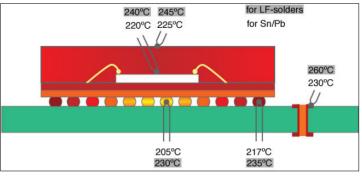

Figure 7-3 Examples of peak reflow temperatures at various locations at or near a BGA

Seate

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

Figure 7-6 Schematic of reflow profile for lead-free assemblies

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

# Solution Contraction Contractic Contraction Contraction Contraction Contraction Contractic

- **Post SMT Process:**

- Conformal coatings

- Underfills

- Corner adhesives

- Inspections

- X-ray

- Visual/Optical

ABOUT THE PRESENTER

Leo Lambert Vice President & Technical Director, EPTAC

## September 2015 Assembly of BGA to the PCB - Section 7

**Rework and Repair**

- Removal and Replacement

- Flux

- Paste

- Hot air system and profiles

Leo Lambert Vice President & Technical Director, EPTAC

## Reliability and Defect Analysis

- Sections 8 discussed the application of the device and its reliability during its functional life.

- The basic thesis being the reliability of the solder joints when exposed to the operation life, thermal cycling and vibration cycling

Leo Lambert Vice President & Technical Director, EPTAC

##

## Reliability and Defect Analysis

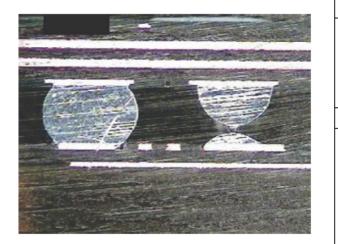

## Section 9, defect and failure analysis

### 9.3.2 Solder Joint Opens Due to Interposer Warp

#### Possible Cause

- The failure appears to be due to insufficient paste release from the stencil or insufficient ball size.

- Warped package (smiling BGA) with comer balls lifted up

#### Potential Solution

- Check balls at incoming prior to assembly.

- Return package to supplier, Implement incoming inspection and or source audit,

Apply extra solder paste on corner lands.

Leo Lambert Vice President & Technical Director, EPTAC

## **Thank You**

## **Questions?**

Leo Lambert Vice President & Technical Director, EPTAC

## **Further Information**

For questions regarding this webinar, please contact Leo Lambert at <u>leo@eptac.com</u> or call at 800-643-7822 ext 215

For information on any of EPTAC's or IPC's Certification Courses, please visit our website at <u>http://www.eptac.com</u>